## Caravel User Guide

#### Resources

#### **Getting Started**

Quickstart: <u>https://caravel-user-project.readthedocs.io/en/latest/</u>

OpenMPW: <u>https://efabless.com/kb-articles/creating-your-first-open-mpw-or-chipignite-project</u> Simulation: <u>https://caravel-user-project.readthedocs.io/en/latest/#running-full-chip-simulation</u>

## Tools

KLayout: https://www.klayout.de/build.html

Docker Desktop: https://www.docker.com/products/docker-desktop/

GTKWave: https://sourceforge.net/projects/gtkwave/files/gtkwave-3.3.100-bin-win64/

Magic: <u>http://opencircuitdesign.com/magic/</u>

#### Reference

User Project: https://caravel-user-project.readthedocs.io/en/latest/ Harness: https://caravel-harness.readthedocs.io/en/latest/ MGMT SoC: https://caravel-mgmt-soc-litex.readthedocs.io/en/latest/ Wishbone Bus: https://cdn.opencores.org/downloads/wbspec\_b4.pdf PDK DRC Rules: https://skywater-pdk.readthedocs.io/en/main/rules/periphery.html OpenRAM: https://vlsi.jp/OpenMPWSRAM\_eng.html#using-sram-with-openmpw Bring-up: https://github.com/efabless/caravel\_board/tree/main

## Project Setup

Clone the required caravel\_user\_project repo from caravel github: <u>https://github.com/efabless/caravel\_user\_project</u>

Before running any simulations or hardening, the following three commands must be run in the root of the caravel repository:

export OPENLANE\_ROOT=\$(pwd)/dependencies/openlane\_src

export PDK\_ROOT=\$(pwd)/dependencies/pdks

export PDK=sky130A

NOTE: This must be done EVERY TIME anything is run, NOT just on setup for the export commands.

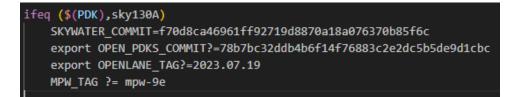

After the root paths are set, we can now build our project. Please ensure that the git commit tags in the root Makefile (seen below) are UP TO DATE with the most recent MPW shuttle branch for the required project submission.

Skywater130A MPW9 Git Commit Tags

Run 'make setup' to install the following:

- Skywater pdk (make pdk-with-volare)

- Openlane (make openlane)

- Submission precheck (make precheck)

While other dependencies and checks are made in make setup, all the required builds will occur here, ensuring you DO NOT need to run any other make command to build the project. If there is an issue with your project build, it is encouraged to delete the dependencies folder and rerun make setup. If that does not work, delete the cloned repsository and start fresh with another 'make setup', ensuring the most up to date commit tags are given in the Makefile, as pulled from the user\_project repo.

# RTL Design

A functional RTL design can be written in Verilog and placed under the /verilog/ folder in the caravel repository. Inside of this folder, the following actions should be made to set up a new RTL design:

- 1. /verilog/rtl

- a. Add the new Verilog designs, can also be in own folder path under /verilog/rtl

- 2. /verilog/includes/includes.gl.caravel\_user\_project

- a. Add "-v \$(USER\_PROJECT\_VERILOG)/gl/design/MODULE.v"

- /verilog/includes/includes.gl+sdf.caravel\_user\_project

Add "\$USER\_PROJECT\_VERILOG/gl/design/MODULE.v"

- 4. /verilog/includes/includes.rtl.caravel\_user\_project

- a. Add "-v \$(USER\_PROJECT\_VERILOG)/rtl/design/MODULE.v"

**NOTE**: For each of the verilog files under /verilog/includes, there MUST be an empty line after the last entry, or the make files for the caravel repository will break.

## **RTL Simulations**

To setup a Verilog testbench in the caravel repository, follow the steps below:

- 1. /verilog/dv/Makefile

- a. Add MODULE name to PATTERNS list in makefile

- 2. /verilog/dv

- a. Copy an existing testcase folder

- b. Rename the new folder to MODULE

- 3. /verilog/dv/MODULE

- a. Rename the copied testbench verilog file and c file to MODULE

- b. Delete all C code from Module.c if only running RTL simulation

- 4. /verilog/dv/MODULE/MODULE\_tb.v

- a. Set name for .vcd file by editing \$dumpfile("MODULE.vcd");

- b. Set name for dumpvars by editing \$dumpvars(o, MODULE\_tb)

- c. Add cmd displays with \$display("STRING") in the testbench if desired

## 23 PATTERNS = io\_ports la\_test1 la\_test2 wb\_port mprj\_stimulus

```

/verilog/dv/Makefile PATTERNS

```

```

initial begin

$dumpfile("backdoor_spi.vcd");

$dumpvars(0, backdoor_spi_tb);

//Repeat cycles of 1000 i_BCLK edges as needed to complete testbench

repeat (10) begin //default 70

repeat (1000) @(posedge i_BCLK);

end

$display("%c[1;31m",27);

`ifdef GL

$display("%c[1;31m",27);

`ifdef GL

$display("Monitor: Timeout, Backdoor SPI (GL) Failed");

`else

$display ("Monitor: Timeout, Backdoor SPI (RTL) Failed");

`endif

$display("%c[0m",27);

$finish;

end

end

```

/verilog/dv/MODULE/MODULE\_tb.v dumpfile, dumpvars, display examples

To run a RTL level simulation from root: "make verify-<module>-rtl"

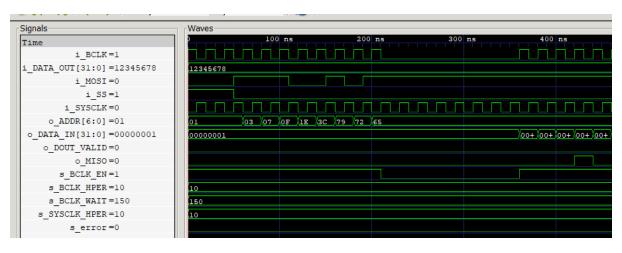

After the RTL simulation is run, you can view the waveform results using the Open-Source tool GTKWave. After opening GTKWave, select File, Open New Tab, and then navigate to the

/verilog/dv/MODULE path. Inside of your module's dv folder, a .vcd file will have been generated, as specified with the \$dumpfile command and name in your testbench. With the vcd file opened, signals can now be appended to be viewed.

# Module Hardening

Functional modules are hardened under the /openlane/ folder in the Caravel repository. The supplied top level design user\_project\_wrapper comes with a set of requirements to pass the eFabless precheck and fabrication and should not be edited. The only Verilog files to add to the top-level module are the top-level functional Verilog files or hardened macros, as referenced below.

It is encouraged to harden your own macros individually, to verify both that they can harden on their own and pass through synthesis, but also in case you want to pass in your hardened design as a drop in macro, which can reduce the amount of resynthesizing of the top-level wrapper.

# To setup a new module for hardening, follow the steps below:

- 1. /openlane/

- a. Copy an existing sample hardening configuration under /openlane/ that is NOT user\_proj\_wrapper

- b. Rename the copied config folder to the same MODULE name as your rtl and dv design

- 2. /openlane/MODULE

- a. Edit config.json with Desired parameters below

- b. Delete pin\_order.cfg if not specifying north/east/south/west side for pin placement

- c. Delete macro.cfg if not placing pre-hardened macro into hardened design

The following parameters inside config.json SHOULD be changed, IF NOT user\_project\_wrapper:

- 1. **DESIGN\_NAME**: name of functional verilog module

- 2. **VERILOG\_FILES**: list of related Verilog files, including submodules instantiated in hardened design

- 3. **CLOCK\_PORT**: Clock input to module for timing analysis

- 4. CLOCK\_NET: Clock Net to module for timing analysis

- 5. **FP\_SIZING**: Determines how length/width of module is determined

- a. Set to "Absolute" for a fixed sized based on DIE\_AREA

- b. Set to "Relative" for optimized size. NOTE: Does not work for designs small enough if you have too many I/o ports

- c. Default is "Relative"

- 6. **DIE\_AREA**: Determines length and width of hardened module if FP\_SIZING set to Absolute

- a. Set to "xo yo x1 y1", or "o o 1000 1000" for area corners

- b. Unit is µm

- 7. PL\_TARGET\_DENSITY: percentage from 0 to 1 of how DENSE cells are in area

- a. Most designs harden up to around 0.6

- b. 1 = closely dense, o = widely spread

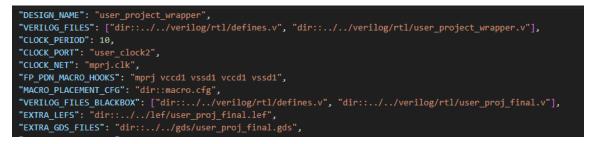

Sample config.json WITHOUT pre-hardened macros

If you are using pre-hardened modules, you should also edit the following config lines:

- 1. VERILOG\_FILES\_BLACKBOX: List each pre-hardened verilog design

- 2. **EXTRA\_LEFS**: List each pre-hardened LEF file /lef/

- 3. EXTRA\_LIBS: List each pre-hardened GDS file under /lib/

- 4. EXTRA\_GDS\_FILES: List each pre-hardened GDS file under /gds/

- 5. MACRO\_PLACEMENT\_CFG: Set to "dir::macro.cfg" for macro placement

```

"DESIGN_NAME": "user_proj_final",

"DESIGN_IS_CORE": 0,

"VERILOG_FILES": ["dir::./../verilog/rtl/defines.v", "dir::../../verilog/rtl/user_proj_final.v"],

"CLOCK_PERIDO": 10,

"CLOCK_PERIDO": 10,

"CLOCK_PORT": "wb_clk_i",

"CLOCK_NET": "backdoor_spi.i_SYSCLK",

"FP_5IZING": "absolute",

"DIE_AREA": "0 0 1200 1200",

"FP_PIN_ORDER_CFG": "dir::pin_order.cfg",

"MACRO_PLACEMENT_CFG": "dir::macro.cfg",

"VERILOG_FILES_BLACKBOX": ["dir::./../verilog/rtl/defines.v",

"VERILOG_FILES_BLACKBOX": ["dir::./../verilog/rtl/defines.v",

"dir::../../verilog/rtl/design/module_control.v",

"dir::../../verilog/rtl/backdoor_spi/backdoor_spi.v"

],

"EXTRA_LEFS": ["dir::../../lef/backdoor_spi.lef",

"dir::../../lef/module_control.lef"

],

"EXTRA_GDS_FILES": ["dir::../../gds/backdoor_spi.gds",

"dir::../../gds/module_control.gds"

],"PL_BASIC_PLACEMENT": 0,

"PL_TARGET_DENSITY": 0.55,

```

Sample config.json WITH pre-hardened macros

**NOTE**: If you are using pre-hardened macros, you MUST specify macro placement in a macro.cfg config file under the folder for your openlane hardening config.

Sample /openlane/user\_project\_wrapper/macro.cfg

Useful Links: <u>https://github.com/The-OpenROAD-</u> <u>Project/OpenLane/blob/master/docs/source/reference/configuration.md</u>

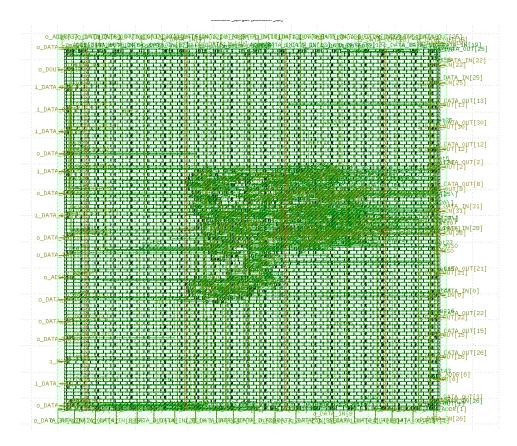

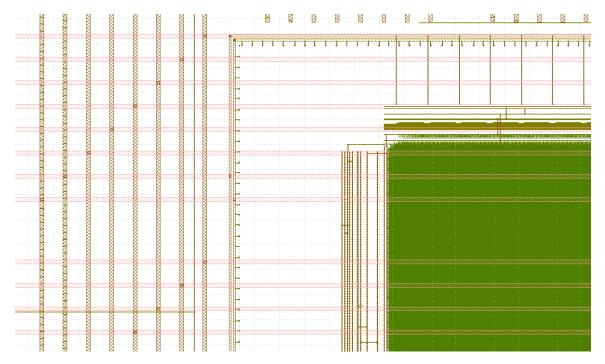

The generated GDS files can be viewed in KLayout. After opening KLayout, select File, Open, and then navigate to the caravel/gds/MODULE.gds to open the hardened macro.

Sample GDS View in KLayout

## Gate Level Simulations

Gate Level simulations are very easy to run if your design has followed the above steps for RTL implementation, RTL simulation, and Module Hardening. At this point, the only thing left to do is run the make verify command with the gl tag, as seen below.

**NOTE**: To run gate level simulations, your design must be successfully hardened. This is because a netlist is generated based on the SkyWater PDK Standard Cell Library, where each of the functional logic gates are pulled from.

To run a GL level simulation from root: "make verify-<module>-gl"

GTKWave can be used to verify your gate level design also, which can be used with the vcd file GL-MODULE.vcd.

| Signals                    | Waves    |         |       |        |     |      |                                                |        |       |      |                      |     |          |           |         |        |         |

|----------------------------|----------|---------|-------|--------|-----|------|------------------------------------------------|--------|-------|------|----------------------|-----|----------|-----------|---------|--------|---------|

| Time                       | ) 1      | 00 ns 2 | 00 ns | 300 ns | 400 | ns 5 | 00 ns                                          | 600    | ns 70 | 0 ns | 800 ns               | 900 | ns 1     | us 1      | .100 ns | 1200 1 | ns 1300 |

| i_BCLK=0                   |          |         |       |        |     |      | ппп                                            |        |       |      | տո                   | ллл |          |           | տիո     |        |         |

| i_DATA_OUT[31:0] =12345678 | 12345678 |         |       |        |     |      |                                                |        |       |      |                      |     |          | FOF       | FOFO    |        |         |

| i_MOSI=1                   |          |         |       |        |     |      |                                                |        |       |      |                      |     |          |           |         |        |         |

| i_SS=0                     |          |         |       |        |     |      |                                                |        |       |      |                      |     |          |           |         |        |         |

| i_SYSCLK=1                 |          | תתתנ    | תתת   | ллл    | uuu | mm   | մՄՄՈ                                           | ЛЛЛ    | JUUU  | תתת  | ллл                  | υυυ | ллл      | התנו      | nn      | տող    | uuu     |

| <pre>o_ADDR[6:0] =65</pre> | 01 +     | ŧŧŧŧ    | + 65  |        |     |      |                                                |        |       |      |                      |     |          | 01        | E E E E | +++6   | 5       |

| o_DATA_IN[31:0] =000000FF  | 00000001 |         |       |        | DĐĐ | ŧŧŧ  | ) <del>(</del> ) <del>(</del> ) <del>(</del> ) | ŧ)ŧ)ŧ) | ÐÐÐÐ  | ĐĐĐĐ | + + <del>+</del> + + |     | + + + FE | F+ 000000 | 001     |        |         |

| <pre>o_DOUT_VALID =0</pre> |          |         |       |        |     |      |                                                |        |       |      |                      |     |          |           |         |        |         |

| o MISO=1                   |          |         |       |        |     |      | лt                                             |        |       |      |                      |     |          |           |         |        |         |

| s BCLK EN=1                |          |         |       |        |     |      |                                                |        |       |      |                      |     |          |           |         |        |         |

| s_BCLK_HPER =10            | 10       |         |       |        |     |      |                                                |        |       |      |                      |     |          |           |         |        |         |

| s BCLK WAIT=150            | 150      |         |       |        |     |      |                                                |        |       |      |                      |     |          |           |         |        |         |

| s_SYSCLK_HPER =10          | 10       |         |       |        |     |      |                                                |        |       |      |                      |     |          |           |         |        |         |

| s error=0                  |          |         |       |        |     |      |                                                |        |       |      |                      |     |          |           |         |        |         |

GL Simulation GTKWave Sample

# Custom Cell Layout – Magic

# Magic

Rationale: Instead of trying to draw the custom cell directly in magic which seemed very imprecise drawing each rectangle by hand, I opted to write a tcl script which would draw rectangles at specific coordinates. In retrospect, the .mag format is simple enough, I could probably have just written the .mag file by hand. However, then the tcl script got too unwieldy, so I created a python script to generate the .tcl file so I could use variables to define the box coordinates easier. This will probably make someone used to TCL cringe, but it worked. Magic must also be built from source, APT version is too old (https://github.com/RTimothyEdwards/magic)

# Resources

https://isn.ucsd.edu/courses/beng207/lectures/Tim\_Edwards\_2021\_slides.pdf

# https://skywater-pdk.readthedocs.io/en/main/rules/periphery.html#npc

https://skywater-pdk.readthedocs.io/en/main/rules/layers.html

# Generation flow

- 1. Run `make setup` to fetch the pdk

- 2. Copy dependencies/pdks/sky130A/libs.tech/magic/sky130A.magicrc to `.magicrc` in the cell generation working directory (`cell\_gen`).

- 3. Run the python script to generate the .tcl file: `python3 NAND.py`

- 4. Open Magic by `cd`ing into cell\_gen and running `magic`. Ensure the PDK environment variables are set.

- 5. Run the tcl script: 'source NAND.tcl'. Make sure you're completely zoomed out when you run that, sometimes if you have zoomed into a certain portion of the design, only that part of the design actually gets erased correctly.

- 6. Update the JSON file in openlane (see below), and create a blackbox verilog file (see Creating the Blackbox below)

- 7. Run the flow (`make user\_proj\_final`). The GDS and LEF files were automatically inserted into openlane, and the .mag file has been saved for future reference.

# LEF Class

There are two main LEF classes, BLOCK and CELL. The custom cell was designated as a CELL, so it will be placed in a row automatically by the detailed placer as expected. BLOCK is used for hardened macros (SRAM, user\_proj\_final, etc) to designate it as a block that should not be placed in a row. There are size constraints on a CELL that are not present in a BLOCK (must fit in an existing row), but BLOCKS cannot be packed as densely.

# Creating the Blackbox

A blackbox verilog file is required to represent the custom cell. The inputs do not all have to be used, but it must have all four power pins (and the LEF/GDS should have all four power pins as well). These pin names must match exactly the names in the LEF/GDS file. A template from our NAND gate is below. One very important feature is the `/// sta-blackbox` which identifies this as a

black box for static timing analysis and LVS check. List this in the openlane JSON file with the gds/lef files (VERILOG\_FILES\_BLACKBOX, EXTRA\_LEFS, and EXTRA\_GDS\_FILES).

# `default\_nettype none /// sta-blackbox `celldefine module NAND ( output X, input A, input B, `ifdef USE\_POWER\_PINS inout VPWR, inout VPB, inout VNB `endif

); assign X = ~(A & B); endmodule

`endcelldefine

`default\_nettype wire

# Tech Issues

The provided SKY130A tech file has an issue that makes all custom cells fail DRC. By DRC rules, two diff layers must have a gap of 27µm. NSDM/PSDM layers must have either no gap or a gap larger than some amount. In the standard cells, the NSDM/PSDM layers are 13.5µm from the end of the DIFF layers, but in the current SKY130A tech file, the NSDM/PSDM layers are auto-generated as a bounding box with a border of 12.5µm. Therefore, if you put the DIFF layers close enough for the PSDM layers to have no gap, the DIFF layers are too close, but if you put the DIFF layers further away, there is a gap in the NSDM layers. To fix this, edit the sky130A tech file in magic to change the 125's to 135's. Because this is re-generated after make setup, you will have to change this whenever using magic after make setup has been run.

| templayer basePSDM pdiffres,mvpdiffres | templayer basePSDM pdiffres,mvpdiffres |  |  |  |  |  |

|----------------------------------------|----------------------------------------|--|--|--|--|--|

| grow 15                                | grow 25                                |  |  |  |  |  |

| or xhrpoly,uhrpoly,xpc                 | or xhrpoly,uhrpoly,xpc                 |  |  |  |  |  |

| grow 110                               | grow 110                               |  |  |  |  |  |

| bloat-or allpactivetap * 125           | bloat-or allpactivetap * 135           |  |  |  |  |  |

| allnactivenontap 0                     | allnactivenontap 0                     |  |  |  |  |  |

| bloat-or allpactivenontap * 125        | bloat-or allpactivenontap * 135        |

|----------------------------------------|----------------------------------------|

| allnactivetap 0                        | allnactivetap 0                        |

| templayer baseNSDM ndiffres,mvndiffres | templayer baseNSDM ndiffres,mvndiffres |

| grow 125                               | grow 135                               |

| bloat-or allnactivetap * 125           | bloat-or allnactivetap * 135           |

| allpactivenontap 0                     | allpactivenontap 0                     |

| bloat-or allnactivenontap * 125        | bloat-or allnactivenontap * 135        |

| allpactivetap 0                        | allpactivetap 0                        |

#### Custom Cell Layout – XSchem

## XSchem

XSchem is a schematic capture tool which will use the base models in the sky130PDK to allow you to simulate a custom cell from basic building blocks. To use XSchem, install from https://xschem.sourceforge.io/stefan/index.html, determine a working directory, and copy the dependencies/pdks/sky130A/libs.tech/xschem/xschemrc file into `.xschemrc`. Ensure the PDK\_ROOT environment variable is set, then run `xschem` from the folder with `.xschemrc`. This will load the sky130A PDK into XSchem.

## Useful Keyboard Shortcuts

U = Undo Shift + U = Redo Shift + I = Insert C = Copy M = Move W = Wire

Shift + W = Snap Wire

#### **Resources on Generating Simulations**

https://xschem.sourceforge.io/stefan/xschem\_man/graphs.html

https://xschem.sourceforge.io/stefan/xschem\_man/tutorial\_run\_simulation.html

## NGSpice Manual

https://ngspice.sourceforge.io/docs/ngspice-41-manual.pdf

#### SKY130 Inverter Reference

http://webo2.gonzaga.edu/faculty/talarico/vlsi/xschemTut.html

#### Running a simulation

Generate a netlist by clicking the Netlist button in the upper right corner, or press `n`.

Run the simulation by clicking the Simulate button in the upper right corner, or run ngspice manually.

Load the waveform by holding ctrl and clicking the Load Waves button to load the waves from the .raw file produced by the simulation.

Double-click the graph body to change the nets shown. Digital mode will stack the graphs as separate waveforms instead of overlapping in space.

# Top Level Wrapper Design

Once all the individual functional designs are complete, you will need to instantiate your design inside of the user\_project\_wrapper Verilog file. It is recommended that you create a wrapper module to be instantiated inside of the user\_project\_wrapper, so that you can harden this design WITHOUT the set requirements of the user\_project\_wrapper, which is used as the top level design for the submission and precheck.

The user\_project\_wrapper has its own specific set of hardening configurations set up under the path /openlane/user\_project\_wrapper. Changing this should be taken with care, since this is used to generate the submission precheck and is used as the top level result for your fabricated design. What you SHOULD edit is the following:

- 1. /openlane/user\_project\_wrapper/config.json

- a. If NOT using pre-hardened macro:

- i. VERILOG\_FILES: include top level module design in wrapper

- b. If using pre-hardened macro:

- i. VERILOG\_FILES\_BLACKBOX: include top level module design in wrapper

- ii. EXTRA\_LEFS: include top level module design in wrapper

- iii. EXTRA\_GDS\_FILES: include top level module design in wrapper

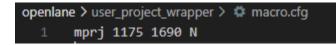

- 2. /openlane/user\_project\_wrapper/macro.cfg

- a. If using pre-hardened macro:

- i. Specify center location of prehardened macro

#### Sample /openlane/user\_project\_wrapper/config.json

| openlane > us | er_proje | ect_wra | pper > | ٥ | macro.cfg |

|---------------|----------|---------|--------|---|-----------|

| 1 mprj        | 1175     | 1690    | N      |   |           |

Sample /openlane/user\_project\_wrapper/macro.cfg

#### SRAM Usage and Integration

#### eFabless SRAM

Utilizing onboard SRAM in the user area can have massive benefits over the DRAM integrated with the management microcontroller. The provider for the memory designs used in the eFabless OpenPDK is another open-source project called OpenRAM. This open-source project is a memory compiler that is capable of building memory macros that you can utilize in your designs. The sddec23-o6 did not do a lot of work with the OpenRAM project other than using their precompiled macros. There is a great deal of customization that is available in the project and is something worth looking at in the future.

# Sourcing the memory design

Now that you have decided to use SRAM in your design the first choice that you must make is where to source your prehardened SRAM macro. There are three primary locations where you can get these designs from. The first is to use the actual OpenRAM tool to generate your own custom design. This method will give you the most flexibility as it will allow you to directly create what you need for your specific design. The only drawback to this method is that it is another tool that you must learn to utilize the memory. The second location is in the OpenPDK that is downloaded when you setup your project. The PDK has four simple designs that you can utilize in your project. This is the most convenient method of getting memory into your project as it is included in the PDK already. However, the one downside to this method is that your memory selection is limited along with bugs existing in PDK version; some of the memories have been bugged for a while and it does not appear to be a priority for eFabless to push out the fixed designs by the OpenRAM team. The third and final way to source your memory designs is to use the designs in the second OpenRAM test chip <u>https://github.com/VLSIDA/openram\_testchip2</u>. This was a test chip designed by the creators of OpenRAM and implements eleven different memory designs. This was the best method that I found for sourcing memory designs as it provided a wide range of designs to choose from. These designs also have the benefit of being designed and verified by the creators of the opensource project; the designers also manually went through the designs by hand to ensure that they would pass future drc and other hardening checks.

#### Bringing the files into your design

Once you have selected your design the next step is to bring all the needed files int your project. The four files that you need are the .gds .lef. .lib and .v files. They should all be place in the corresponding folders with the Verilog file placed in your rtl folder.

| ∼ rtl                                 |  |

|---------------------------------------|--|

| > backdoor_spi                        |  |

| > design                              |  |

| > dsp                                 |  |

| ≣ defines.v                           |  |

| ■ openram_defines.v                   |  |

| ≣ sky130_sram_1kbyte_1rw1r_8x1024_8.v |  |

Lib location

| $\sim$ lef        |                        |

|-------------------|------------------------|

| ≣ NAND.lef        |                        |

| ≣ SIGN.lef        |                        |

| sky130_fd_sc_hdl  | _clkmux2_1.lef         |

| ≣ sky130_sram_1kb | yte_1rw1r_8x1024_8.lef |

| Lef location      |                        |

| ∨ ads             |                        |

| - gas                                   |

|-----------------------------------------|

| ≣ NAND.gds                              |

| ≣ SIGN.gds                              |

| ≣ sky130_fd_sc_hdllclkmux2_1.gds        |

| ≣ sky130_sram_1kbyte_1rw1r_8x1024_8.gds |

Gds location

With all these folders added to your design you are ready to start integrating the memory into your rtl design.

#### RTL design

Implementing and using the memory is straight forward using the functional model provided in the design Verilog file. The first thing you must do though while designing with the memory is to place it in the user\_project\_wrapper and to interact with it there. The reasoning behind this will be explained in the hardening section as that is the time where the SRAM location matters. With the memory placed in the correct location you can start to hook up ports to the design. The first two that need to be connected are the power and ground connections called vccd1 and vssd1. These are important connections and need to be connected to either the vccd1 and vssd1 or vccd2 and vssd2 provided by the wrapper. The next ports to hook up are the clock ports to your desired clock signal. From there the next port to hook up is the chip select line to enable the memory. The next port to connect is the write enable port that will control whether the memory is reading from or writing to memory. From there we can hook up the address port to your address driver. The last two ports to hook up are the data in and data out ports that provide your data connection to the memory.

One niche thing about the memory is that it will have a three-cycle delay after the address is read in before the data is stored in the memory or able to be read from the memory. You must keep this in mind while designing with the memory. With this caveat in mind and having the memory ports hooked up you can implement it in your design however you see fit.

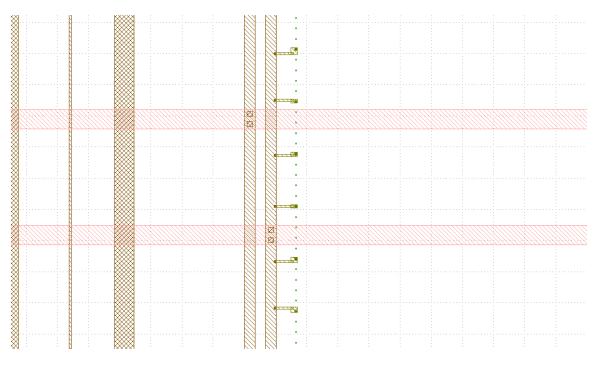

## Hardening the SRAM

Once you have completed your rtl design with memory the next step is to go through the hardening process. The first step in this process is to modify / replace the config.json file for the user\_project\_wrapper hardening process. I would suggest that you use the config.json file from either sddec23-o6's repo or from the second OpenRAM test chip

https://github.com/VLSIDA/openram\_testchip2. The reason for this is because there are multiple settings that need to be configured so that the memory will properly harden. During our initial attempts we were struggling to get the memory to properly hook up to the power rails. This issue was caused by the fact that we were instantiating the memory inside of another macro. This was problematic as the SRAM needs access to the top metal layer met5 for its power connections. When the macro was connected to the met5 layer it was able to be placed into the user\_project\_wrapper.

The main items that need to be set in the file are FP\_PDN\_CHECK\_NODES,

FP\_PDN\_ENABLE\_RAILS, RUN\_FILL\_INSERTION, and RUN\_TAP\_DECAP\_INSERTION. With all of these sets the memory should be able to properly harden and you should be able to see in the created gds file that the power rings of the memory module are connected to top met5 power layer.

Power Rail Connection

Zoomed In Power Rail Connection.

## EFabless Submission Precheck

The MPW Precheck is a SEPERATE Github repository that can be cloned using the root makefile in the caravel repository. This is used to compare the hardened result of user\_project\_wrapper, our top-level module, against multiple different requirements for project submission. As long as the design fits all functional requirements, AND passes this precheck, a design is ready for submission.

To clone the MPW precheck github repository: 'make precheck'

To run the MPW Precheck: 'make run-precheck'

**NOTE**: The top-level wrapper user\_project\_wrapper must be hardened with 'make user\_project\_wrapper' before a precheck can occur.

## Modifying project to pass precheck parameters:

- 1. Documentation Pass

- a. The root README.md file must be modified to ensure documentation has been updated

- b. For a minimum pass, delete all existing contents and add custom header title

- 2. GPIO Pass

- a. Update GPIO INIT config from INVALID for following file:

- i. sddec23-06/verilog/rtl/user\_defines.v

- b. Can set to either inputs, outputs, bidirectional, or analog pins

## Troubleshooting Notes

#### LINTER: Mixing positional and .\*/named instantiation connection

- `ifdef USE\_POWER\_PINS must be the first items in the module port list, for some reason it gets angry if you put the power pins last.

# Supported Verilog (\* attributes \*)

- <u>https://github.com/The-OpenROAD-Project/yosys/blob/master/README.md#verilog-attributes-and-non-standard-features</u>

#### What is maglef vs lef?

Best guess is according to <u>https://github.com/The-OpenROAD-</u>

<u>Project/OpenLane/issues/1067</u>, some of the older PDK's had a set of LEF issues, maglef is

LEF files re-exported using Magic to hopefully fix most of those issues.